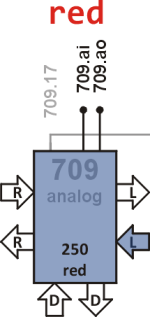

Node 709

This node generates red component of bright pixels and black color of dark pixels. It receives character slice bitmap and color, and sets analog output pin to appropriate voltages. Start of rendering is triggered by character clock on shared pin 17. Timing of individual pixels is managed by delay loops.

Source code

trg 00 dup !b left dup ! ;

pix 03 -if over !b ; then a !b . ;

go 06 3 push trg a! @ color @ char 15555 a!

begin 2* pix 17 for unext next

5th pixel 2* pix 5 for unext

drop drop over or up a! go ; 17

init io b! up a! 800 15555 go ; 1E

1 r 0 u 0 ether

Definitions

- trg

- Set WD bit low/high, and DAC to 0 V (black color), prepare LEFT on stack (we'll store LEFT in A when back from trg), and store a dummy word to UP (thus suspend till rising/falling char clock edge according to the current WD bit state).

- pix

- Store color component (in S) to DAC if current pixel is bright (T17 set), else store black.

- go

- Prepare loop parameter for 4 pixels, wait for trg, fetch color and character slice from LEFT, set A to black, begin loop. Shift next pixel to T17, display with pix, wait one pixel time, and repeat. Render the 5th pixel with pix, drop both char and color from stack, toggle WD bit with mask in S, set A back to UP and jump to go.

- init

- Set registers A and B, put mask for WD bit and black color value on stack, and jump to go.

Description

This node generates red component of VGA signal. Word go prepares loop index in return stack and calls word trg. It sets DAC to black color, and waits for an edge (both rising and falling edges are active) on shared pin 17, which signalizes start of a character. Then two words are fetched from node 710; red color component and a character slice bitmap. For each pixel the slice is shifted left, so that the pixel to be displayed is in bit T17. If set, word pix sets DAC to color (value held in S), or to black (value 15555 stored in A). Back in go a delay till the end of the pixel is timed out with 18 cycles of for unext loop. Note that overall duration of the pixel (83 ns) includes also the code executed in pix.

Four pixels are displayed this way, the 5th pixel needs only 6 cycles of for unext dealy loop as the rest is timed out by the code that toggles WD bit and prepares stack for the next slice. The last pixel (always black) is displayed when trg starts executing. Its width corresponds to the time remaining till the next char clock edge.